# S30MS-P ORNAND™Flash Family

S30MS01GP, S30MS512P 1Gb/512Mb, x8/x16, 1.8 Volt NAND Interface Memory Based on MirrorBit<sup>™</sup> Technology

Data Sheet (Preliminary)

Notice to Readers: This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See Notice On Data Sheet Designations for definitions.

### **Notice On Data Sheet Designations**

Spansion LLC issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Spansion LLC is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Spansion LLC therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Spansion LLC. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed product without notice."

#### **Preliminary**

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Spansion product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or  $V_{IO}$  range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion LLC applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Spansion product(s) described herein. Spansion LLC deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

# S30MS-P ORNAND<sup>TM</sup> Flash Family

S30MS01GP, S30MS512P 1Gb/512Mb, x8/x16, 1.8 Volt NAND Interface Memory Based on MirrorBit<sup>™</sup> Technology

Data Sheet (Preliminary)

### **Distinctive Characteristics**

- Single Power Supply Operation

- 1.8 volt read, erase, and program operations

- $V_{CC} = 1.7 \text{ to } 1.95 \text{V}$

- Manufactured on 90 nm MirrorBit<sup>TM</sup> Process Technology

- Bus widths x8 and x16

- Page Size

- Full Page Read

- 2K + 64 Byte

- Partial Page Read512 + 16 Byte

- Block (erase unit) Architecture

- Number of Blocks

1Gb: 1K blocks

512Mb: 512 blocks

- Block Size128K + 4K Byte

- Compatibility with NAND Flash I/O

- Provides pinout and command set compatibility with single-power supply NAND flash

- High-Performance Cache Register

- Cache Register matches page size to improve programming throughput

- 100,000 Program/Erase Cycles per Sector Typical

- 10-Year Data Retention Typical

- **■** Operating Temperature Ranges

- Wireless (-25°C to +85°C)

- Package options

- 48-pin TSOP

- 137-ball FBGA MCP Compatible

- 100% Valid Blocks

### **Performance Characteristics**

| Read Access Times (Maximum) |       |  |  |

|-----------------------------|-------|--|--|

| Full Page Random Access     | 25 µs |  |  |

| Partial Page Random Access  | 8 µs  |  |  |

| Serial Read                 | 25ns  |  |  |

| Current Consumption (typical) |       |

|-------------------------------|-------|

| Read Current                  | 40 mA |

| Erase Current                 | 60 mA |

| Program Current               | 60 mA |

| Standby Current               | 10 uA |

| Read, Program and Erase Performance (typical) |           |           |  |  |  |

|-----------------------------------------------|-----------|-----------|--|--|--|

| x8 x16                                        |           |           |  |  |  |

| Program                                       | 2.3 MB/s  | 2.4 MB/s  |  |  |  |

| Erase                                         | 2.7 MB/s  | 2.7 MB/s  |  |  |  |

| Full Page Read                                | 26.7 MB/s | 40.1 MB/s |  |  |  |

| Partial Page Read                             | 24.3 MB/s | 34.9 MB/s |  |  |  |

Leaend:

b = bit, B = Byte, K = 1024, M = 1048576

### **Contents**

| וופוש          |                                                              | iidideleiisiies                                                                                                                                                                                                                  |                                        |

|----------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Perf           | ormance                                                      | Characteristics                                                                                                                                                                                                                  | 1                                      |

| 1.             | General                                                      | Description                                                                                                                                                                                                                      | 4                                      |

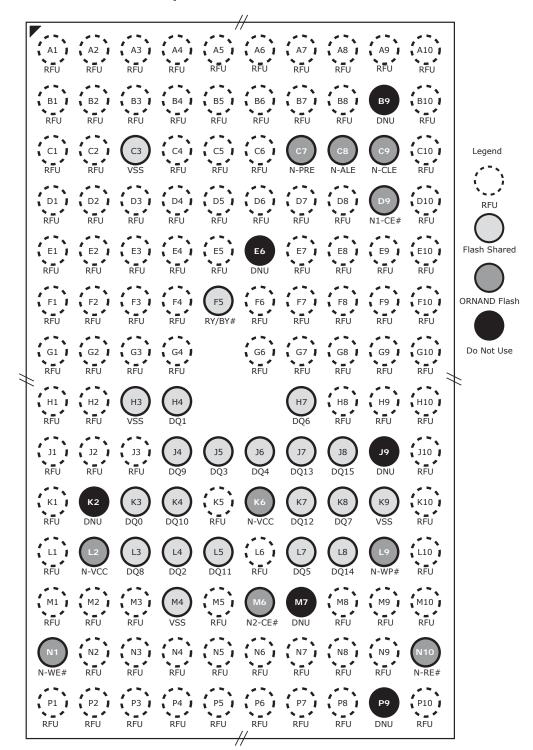

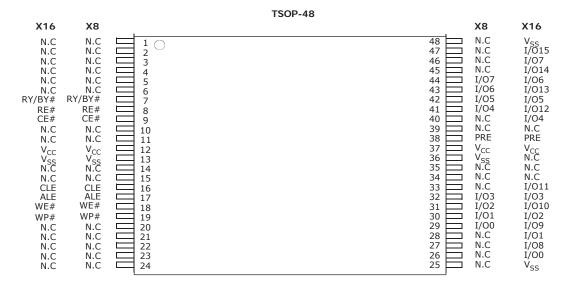

| 2.             | 2.1<br>2.2                                                   | tion Diagrams  137-Ball MS01GP MCP-Compatible FBGA Pinout  MS01GP and MS512P 48-Pin TSOP Pinout                                                                                                                                  | 5                                      |

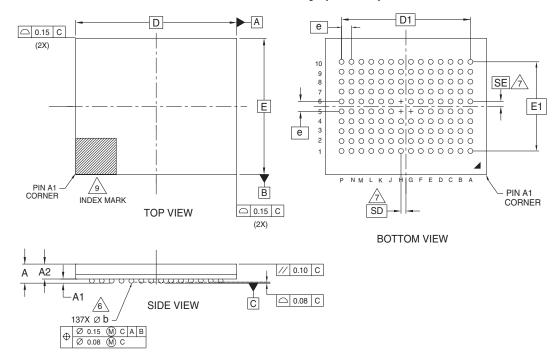

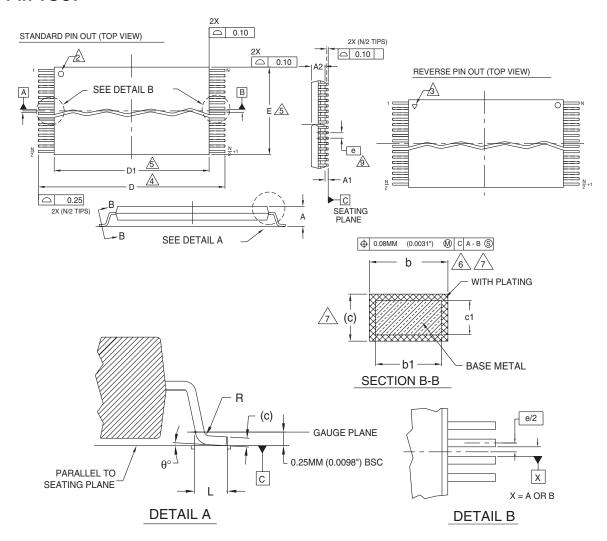

| 3.             | 9.1<br>3.2                                                   | I <b>l Dimensions</b> VBP137—137-Ball Fine Pitch Ball Grid Array (FBGA)  48-Pin TSOP                                                                                                                                             | 7                                      |

| 4.             | <b>Pin Nan</b><br>4.1<br>4.2                                 | nes and Descriptions.  Pin Names and Functions.  Pin Descriptions.                                                                                                                                                               | 9                                      |

| 5.             | Block D                                                      | iagram 1                                                                                                                                                                                                                         | 10                                     |

| 6.             | Absolut                                                      | e Maximum Ratings 1                                                                                                                                                                                                              | 10                                     |

| 7.             | Orderin<br>7.1                                               | g Information                                                                                                                                                                                                                    |                                        |

| 8.             | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8         | al Specifications  Absolute Maximum Ratings Capacitance (Ta = 25°C, f = 1 MHz)  Valid Blocks  Recommended DC Operating Conditions  DC Characteristics  AC Characteristics  AC Test Conditions  Program and Erase Characteristics | 12<br>12<br>13<br>13                   |

| 9.             |                                                              | Diagrams                                                                                                                                                                                                                         | 15                                     |

| 10.            | • • • • • • • • • • • • • • • • • • • •                      | Atray Organization                                                                                                                                                                                                               | 23                                     |

| 11.            | Operation                                                    | on Mode: Logic and Command Tables                                                                                                                                                                                                | 25                                     |

| 12.            | 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8 | Operation2Read Mode2Page Program2Cache Program2Page Duplicate Program2Block Erase3Write Operation Status3Status Read3Reset3                                                                                                      | 26<br>27<br>28<br>29<br>30<br>30<br>30 |

| 13.            | 13.1<br>13.2                                                 | tion Notes                                                                                                                                                                                                                       | 33                                     |

| 14.            | _                                                            | n History                                                                                                                                                                                                                        |                                        |

| Table<br>Table | e 9.2                                                        | ID Byte Settings Summary                                                                                                                                                                                                         | 22                                     |

|                |                                                              | -                                                                                                                                                                                                                                |                                        |

**Tables**

### Data Sheet (Preliminary)

| Table 10.1   | Memory Addressing Key                                                    |

|--------------|--------------------------------------------------------------------------|

| Table 10.2   | (1Gb) x 8 device                                                         |

| Table 10.3   | (512Mb) x8 Addressing                                                    |

| Table 10.4   | (1Gb) x 16 Addressing                                                    |

| Table 10.5   | (512) x 16 Addressing                                                    |

| Table 11.1   | Operation Table                                                          |

| Table 11.2   | Command Table                                                            |

| Table 11.3   | Read Mode Operation Status                                               |

| Table 12.1   | Page Segments27                                                          |

| Table 12.2   | Status Output Table                                                      |

|              |                                                                          |

|              |                                                                          |

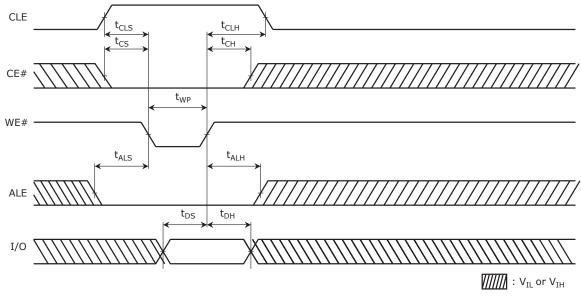

| Figure 9.1   | Command Input Cycle Timing Diagram                                       |

| Figure 9.2   | Address Input Cycle Timing Diagram                                       |

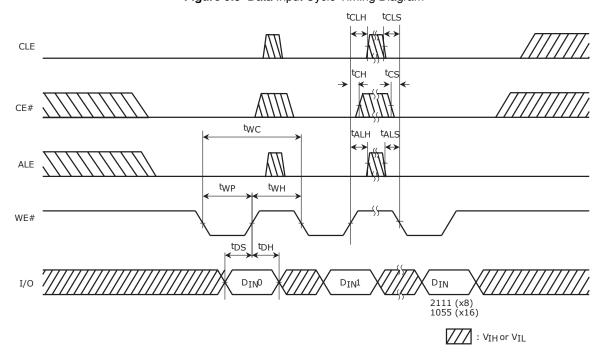

| Figure 9.3   | Data Input Cycle Timing Diagram                                          |

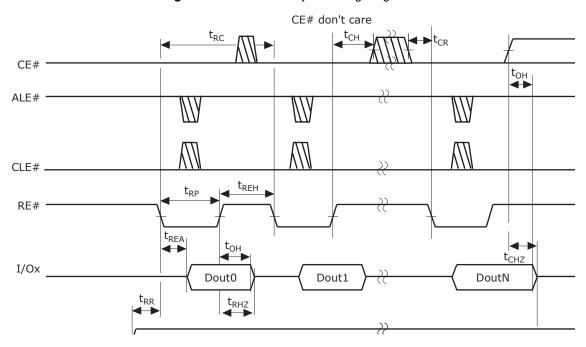

| Figure 9.4   | Serial Read Cycle Timing Diagram                                         |

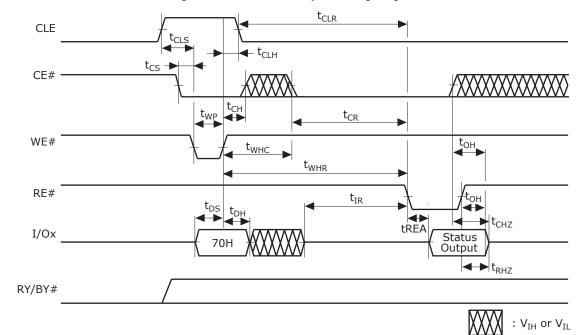

| Figure 9.5   | Status Read Cycle Timing Diagram                                         |

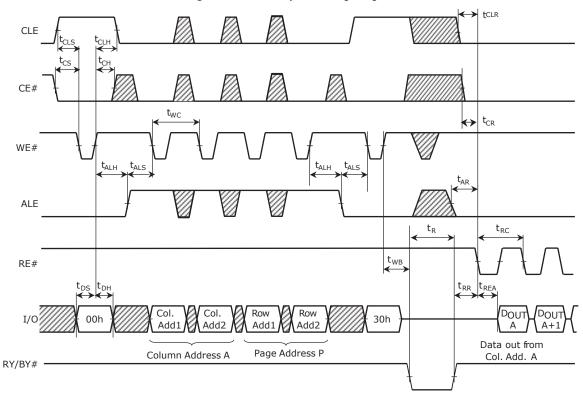

| Figure 9.6   | Read Cycle Timing Diagram                                                |

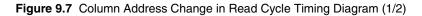

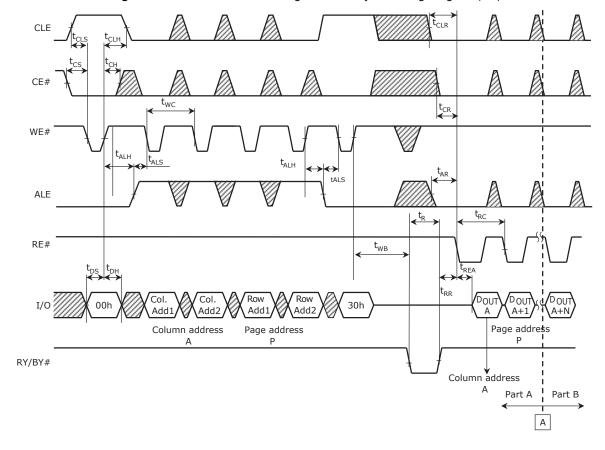

| Figure 9.7   | Column Address Change in Read Cycle Timing Diagram (1/2)                 |

| Figure 9.8   | Column Address Change in Read Cycle Timing Diagram (2/2)                 |

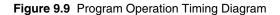

| Figure 9.9   | Program Operation Timing Diagram                                         |

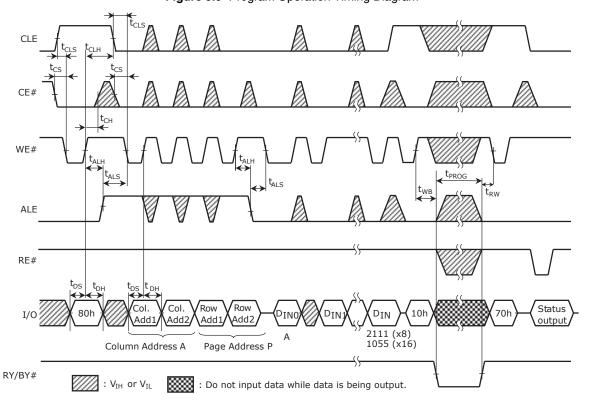

| Figure 9.10  | Block Erase Timing Diagram                                               |

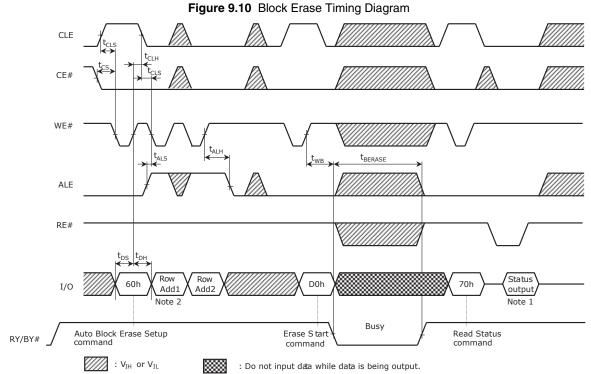

| Figure 9.11  | Cache Program Operation Timing Diagram                                   |

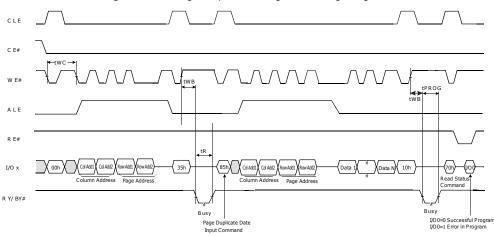

| Figure 9.12  | Page Duplicate Program Timing Diagram                                    |

| Figure 9.13  | ID Read Operation Timing Diagram                                         |

| Figure 10.1  | Array Organization                                                       |

| Figure 12.1  | Read Mode                                                                |

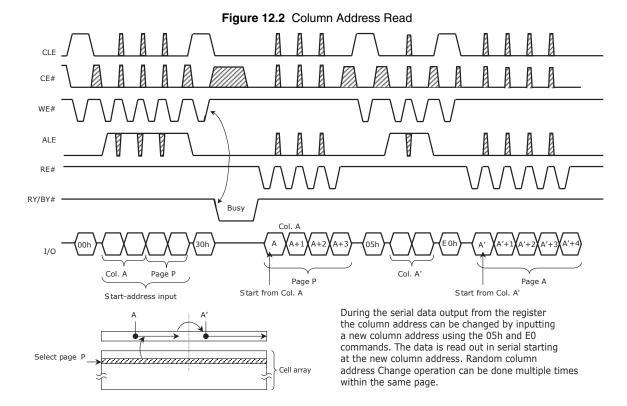

| Figure 12.2  | Column Address Read                                                      |

| Figure 12.3  | Page Program                                                             |

| Figure 12.4  | Serial Input Command Sequence                                            |

| Figure 12.5  | Cache Program                                                            |

| Figure 12.6  | Page Duplicate Program Operation                                         |

| Figure 12.7  | Page Duplicate Program Operation with Random Data Input                  |

| Figure 12.8  | Block Erase 30                                                           |

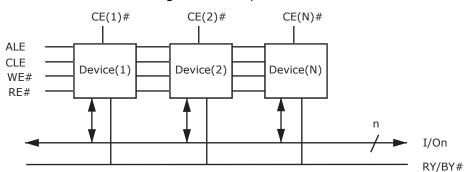

| Figure 12.9  | Multiple Devices                                                         |

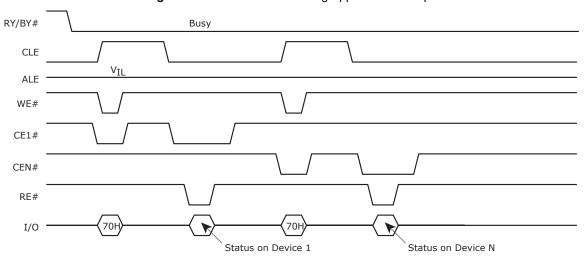

|              | Status Read Timing Application Example                                   |

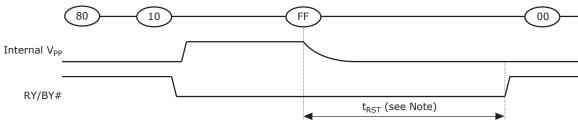

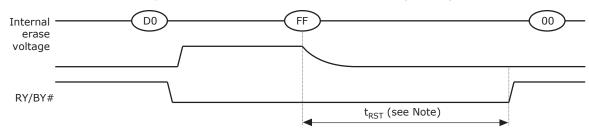

| Figure 12.11 | Reset (FFh) Command Input During Programming                             |

| -            | Reset (FFh) Command Input During Erasing                                 |

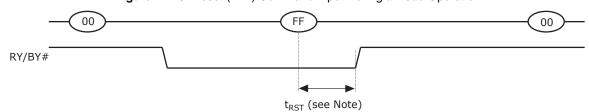

|              | Reset (FFh) Command Input During a Read Operation                        |

| Figure 12.14 | Reset (FFh) Command During Operations Other Than Program, Erase, or Read |

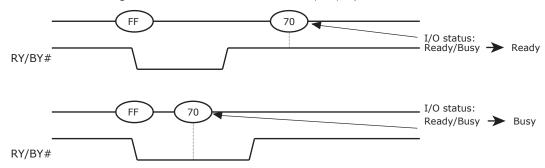

| Figure 12.15 | Status Read Command (70h) Input After a Reset                            |

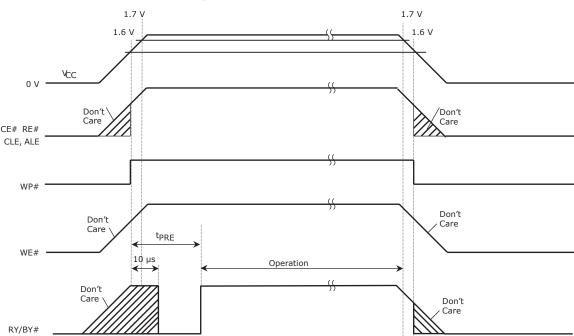

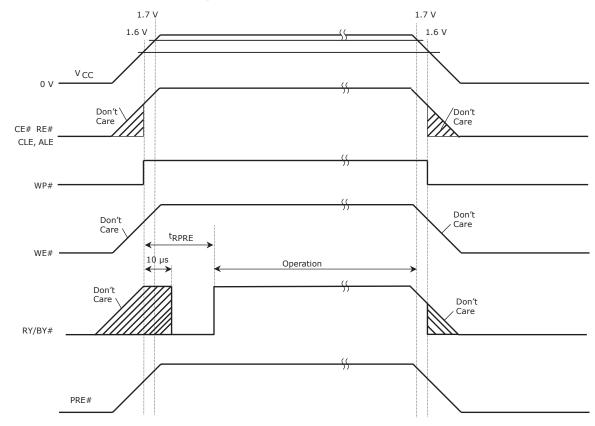

| Figure 13.1  | Power-On/Off Sequence                                                    |

| Figure 13.2  | Power-On Auto-read Enable                                                |

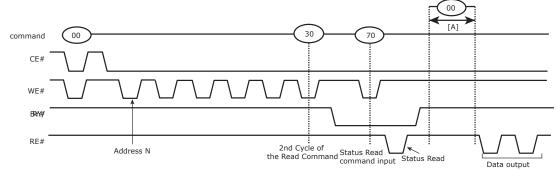

| Figure 13.3  | Status Read During a Read Operation                                      |

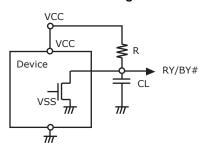

| Figure 13.4  | RY/BY#: Termination for the Ready/Busy Pin (RY/BY#)                      |

| Figure 13.5  | WP# Signal—Low                                                           |

**Figures**

### 1. General Description

The S30MS-P is a 1.8V single voltage flash memory product manufactured using 90 nm MirrorBit™ technology. The S30MS01GP is a 1Gb device, organized as 64M Words or 128MB. The S30MS512P is a 512Mb device, organized as 32M Words or 64MB.

The S30MS-P family of devices offer advantages such as:

- Fast write and sustained write speed suitable for data storage applications

- Fast read speed and reliability suitable for demanding code storage applications

- Proven MirrorBit<sup>™</sup> technology

The devices are offered in a 48-pin TSOP, or FBGA MCP-compatible packages. Each device has separate chip enable (CE#) controls for the FBGA package.

The S30MS-P is a byte/word serial-type memory device that utilizes the I/O pins for both address and data input/output, as well as for command input. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state disks, pictures storage for still cameras, cellular phones, and other systems that require high-density non-volatile data storage.

Typical application requirements are shown in the table below with reference to the ORNAND capabilities.

| Application          | Minimum Requirements   | Spansion ORNAND |  |

|----------------------|------------------------|-----------------|--|

| 2G Network           | 14.4 Kbps (1.8 KB/sec) | ✓               |  |

| 3G Network           | 2 Mbps (250 KB/sec)    | ✓               |  |

| 3.5G Network (HSPDA) | 2.5 MB/sec             | ✓               |  |

| Full Speed USB       | 1.5 MB/sec             | ✓               |  |

| MP3 Playback         | 320 Kbps (40 KB/sec)   | <b>√</b>        |  |

| MPEG2 (H.262)        | 3 MB/sec               | ✓               |  |

| MPEG4 (H.264)        | 1 MB/sec               | ✓               |  |

| WiMax                | 0.25 MB/sec            | ✓               |  |

The devices include the following features:

- Automatic page 0 read, allows access of the data in page 0 without command and address input of read command after power-up

- Chip Enable Don't Care support for direct connection with microcontrollers

- Compatible with NAND Flash command set. Commands are written to the device using standard microprocessor write timing. Write cycles provide commands, addresses and data

- Initiation of program and erase functions through command sequences. Once a program or erase operation begins, the host system should only poll for status or monitor the Ready/Busy# (RY/BY#) output to determine whether the operation is complete

- Manufactured using MirrorBit<sup>™</sup> flash technology resulting in the highest levels of quality, reliability, and cost effectiveness

## 2. Connection Diagrams

## 2.1 137-Ball MS01GP MCP-Compatible FBGA Pinout

### 2.2 MS01GP and MS512P 48-Pin TSOP Pinout

### 3. Physical Dimensions

## 3.1 VBP137—137-Ball Fine Pitch Ball Grid Array (FBGA)

| PACKAGE | VBP 137                            |     |                                 |                             |                             |

|---------|------------------------------------|-----|---------------------------------|-----------------------------|-----------------------------|

| JEDEC   | N/A                                |     |                                 |                             |                             |

|         | 13.00 mm x 11.00 mm NOM<br>PACKAGE |     | m NOM                           |                             |                             |

| SYMBOL  | MIN                                | NOM | MAX                             | NOTE                        |                             |

| Α       |                                    |     | 1.00                            | OVERALL THICKNESS           |                             |

| A1      | 0.17                               |     |                                 | BALL HEIGHT                 |                             |

| A2      | 0.60                               |     | 0.76                            | BODY THICKNESS              |                             |

| D       | 13.00 BSC.                         |     |                                 | BODY SIZE                   |                             |

| Е       | 11.00 BSC.                         |     |                                 | BODY SIZE                   |                             |

| D1      | 10.40 BSC.                         |     |                                 | BALL FOOTPRINT              |                             |

| E1      | 7.20 BSC.                          |     |                                 | BALL FOOTPRINT              |                             |

| MD      | 14                                 |     | MD 14 ROW MATRIX SIZE D DIRECTI |                             | ROW MATRIX SIZE D DIRECTION |

| ME      |                                    | 10  |                                 | ROW MATRIX SIZE E DIRECTION |                             |

| N       | 137                                |     | N 137 TOTAL BALL COUNT          |                             | TOTAL BALL COUNT            |

| φb      | 0.35 0.40 0.45                     |     | 0.45                            | BALL DIAMETER               |                             |

| е       | 0.80 BSC.                          |     |                                 | BALL PITCH                  |                             |

| SD/SE   | 0.40 BSC.                          |     |                                 | SOLDER BALL PLACEMENT       |                             |

|         | G5,H5,H6                           |     |                                 | DEPOPULATED SOLDER BALLS    |                             |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JESD 95-1, SPP-010 (EXCEPT AS NOTED).

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL ROW MATRIX SIZE IN THE "D" DIRECTION.

- SYMBOL "ME" IS THE BALL COLUMN MATRIX SIZE IN THE "E" DIRECTION.

N IS THE TOTAL NUMBER OF SOLDER BALLS.

6 DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

DIAMETER IN A PLANE PARALLEL TO DATUM C.

7 SD AND SE ARE MEASURED WITH RESPECT TO DATUMS

A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW PARALLEL TO THE D OR E DIMENSION, RESPECTIVELY, SD OR SE = 0.000.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, SD OR SE =  $\boxed{6/2}$

- 8. NOT USED.

- 9. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

- A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK

MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

3549 \ 16-038.25 \ 2.16.6

#### 3.2 48-Pin TSOP

| Package | TS/TSR 048 |          |       |  |

|---------|------------|----------|-------|--|

| Jedec   | MC         | -142 (D) | DD    |  |

| Symbol  | MIN        | NOM      | MAX   |  |

| А       | _          | _        | 1.20  |  |

| A1      | 0.05       | _        | 0.15  |  |

| A2      | 0.95       | 1.00     | 1.05  |  |

| b1      | 0.17       | 0.20     | 0.23  |  |

| b       | 0.17       | 0.22     | 0.27  |  |

| c1      | 0.10 —     |          | 0.16  |  |

| С       | 0.10       | _        | 0.21  |  |

| D       | 19.80      | 20.00    | 20.20 |  |

| D1      | 18.30      | 18.40    | 18.50 |  |

| E       | 11.90      | 12.00    | 12.10 |  |

| е       | 0.50 BASIC |          |       |  |

| L       | 0.50       | 0.60     | 0.70  |  |

| θ       | 0°         | _        | 8°    |  |

| R       | 0.08       | 0.20     |       |  |

| N       | 48         |          |       |  |

CONTROLLING DIMENSIONS ARE IN MILLIMETERS (mm).

(DIMENSIONING AND TOLERANCING CONFORMS TO ANSI Y14.5M-1982)

PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE UP).

PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE DOWN), INK OR LASER MARK.

TO BE DETERMINED AT THE SEATING PLANE [-C-]. THE SEATING PLANE IS DEFINED AS THE PLANE OF CONTACT THAT IS MADE WHEN THE PACKAGE LEADS ARE ALLOWED TO REST FREELY ON A FLAT HORIZONTAL SURFACE. 4

DIMENSIONS D1 AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTUSION IS

DIMENSION b DOES NOT INCLUDE DAMBAR PROTUSION. ALLOWABLE DAMBAR PROTUSION SHALL BE 0.08 (0.0031\*) TOTAL IN EXCESS OF b DIMENSION AT MAX. MATERIAL CONDITION. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD TO BE 0.07 (0.0028\*).

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10MM (.0039") AND 0.25MM (0.0098") FROM THE LEAD TIP.

LEAD COPLANARITY SHALL BE WITHIN 0.10mm (0.004") AS MEASURED FROM THE SEATING PLANE.

DIMENSION "e" IS MEASURED AT THE CENTERLINE OF THE LEADS.

3355 \ 16-038.10c

# 4. Pin Names and Descriptions

### 4.1 Pin Names and Functions

| Pin Name        | Pin Function         |  |

|-----------------|----------------------|--|

| I/O0 to I/O15   | Data Input/Output    |  |

| CLE             | Command Latch Enable |  |

| ALE             | Address Latch Enable |  |

| CE#, CE1#, CE2# | Chip Enable          |  |

| RE#             | Read Enable          |  |

| WE#             | Write Enable         |  |

| WP#             | Write Protect        |  |

| PRE             | Power on Read Enable |  |

| RY/BY#          | Ready/Busy Output    |  |

| V <sub>CC</sub> | Power                |  |

| V <sub>SS</sub> | Ground               |  |

| N.C.            | No Connection        |  |

# 4.2 Pin Descriptions

The device is a byte/word serial access memory that utilizes time-sharing input of address information. The device pin-outs are configured as shown in 137-Ball MS01GP MCP-Compatible FBGA Pinout on page 5.

| Pin             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLE             | Command Latch Enable: The CLE input signal is used to control loading of the operation mode command into the internal command register. The command is latched into the command register from the I/O port on the rising edge of the WE# signal while CE# is low and CLE is High.                                                                                                                                                                                     |

| ALE             | Address Latch Enable: The ALE signal is used to control loading of either address information or input data into the internal address/data register. Address information is latched on the rising edge of WE# if CE# is low and ALE is High.                                                                                                                                                                                                                          |

|                 | Input data is latched if CE# is low and ALE is Low.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CE#, CE1#, CE2# | Chip Enable: The device enters a low-power Standby mode when the device is in Ready mode. The CE# signal is ignored when the device is in a Busy state (RY/BY# = L), such as during a Page Buffer Load or Erase operation, and will not enter Standby mode even if the CE# input goes high. The CE# signal may be inactive during the Page Buffer write and Page Buffer load of the array data. The 2Gb device has two chip enable pins: CE1# and CE2# (one per die). |

| WE#             | Write Enable: The WE# signal is used to control the acquisition of data from the I/O port.                                                                                                                                                                                                                                                                                                                                                                            |

| RE#             | Read Enable: The RE# signal controls serial data output. Data is available t <sub>REA</sub> after the falling edge of RE#. The internal column address counter is also incremented (Address = Address + 1) on this falling edge.                                                                                                                                                                                                                                      |

| I/O0 to I/O7    | I/O Port: The I/O0 to I/O7 pins are used as a port for transferring address, command, and input/output data to and from the device.                                                                                                                                                                                                                                                                                                                                   |

| I/O8 to I/O15   | I/O Port: The I/O8 to I/O15 pins are used as a port for transferring input/output data to and from the device in x16 mode only. I/O8 to I/O15 pins must be low level during address and command input.                                                                                                                                                                                                                                                                |

| WP#             | Write Protect: The WP# signal is used to protect the device from accidental programming or erasing. This signal is usually used for protecting the data during the power-on/off sequence when input signals are invalid.                                                                                                                                                                                                                                              |

| RY/BY#          | Ready/Busy:The RY/BY# output signal is used to indicate the operating condition of the device. The RY/BY# signal is in Busy state (RY/BY# = L) during the Program, Erase, and Read operations and return to Ready state (RY/BY# = H) after completion of the operation. The output buffer for this signal is an open drain.                                                                                                                                           |

| PRE             | <b>Power-on Read Enable</b> : The PRE controls auto read operation executed during power-on. The power-on autoread is enabled when PRE pin in tied to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                               |

| V <sub>SS</sub> | Ground: V <sub>SS</sub> is the Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| N.C             | No Connection: Lead is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                      |

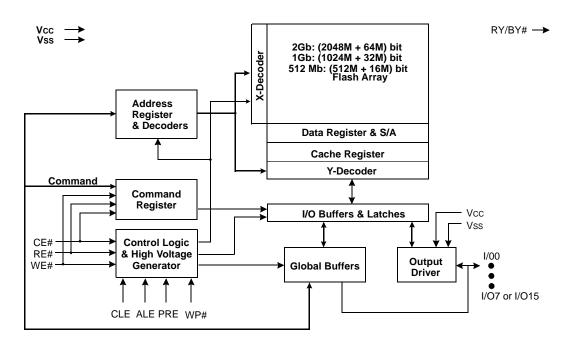

### 5. Block Diagram

# 6. Absolute Maximum Ratings

| Parameter                          | Symbol              | Rating                                                                    | Unit |

|------------------------------------|---------------------|---------------------------------------------------------------------------|------|

| Voltage on any pin relative to Vss | V <sub>IN/OUT</sub> | -0.5 to Vcc + 0.5                                                         | V    |

| voltage on any pin relative to vss | V <sub>CC</sub>     | -0.5 to + 2.5                                                             | V    |

| Storage Temperature                | T <sub>STG</sub>    | -65 to +150                                                               | °C   |

| Operating Temperature              | T <sub>OPR</sub>    | 0 to +70 (Commercial)<br>-40 to +85 (Industrial)<br>-25 to +85 (Wireless) | °C   |

| Temperature under bias             | T <sub>BIAS</sub>   | -65 to 125                                                                | °C   |

| Short circuit current              | I <sub>os</sub>     | 5                                                                         | mA   |

#### Notes:

- 1. Minimum DC voltage is -0.6v on input/output pins. During transitions, this level may undershoot to -2.0v for periods <30ns.

- $2. \ \ \textit{Maximum DC voltage on input/output pins is Vcc+0.3v which, during transitions, may overshoot to Vcc+2.0v for periods < 20 ns. \\$

- 3. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as details in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

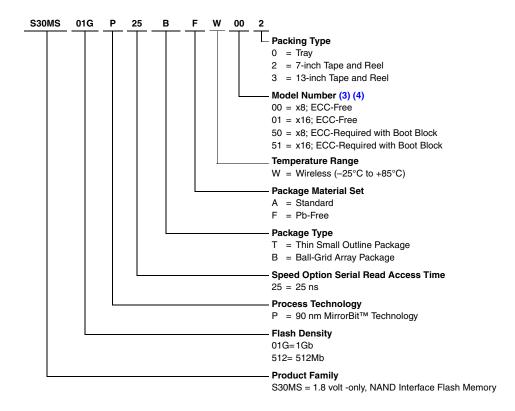

# 7. Ordering Information

The order number is formed by a valid combinations of the following:

### 7.1 Valid Combinations

Valid Combination list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Valid Combinations           |                 |                                               |                 |                 |                 |

|------------------------------|-----------------|-----------------------------------------------|-----------------|-----------------|-----------------|

| Base Ordering<br>Part Number | Speed<br>Option | Package Type, Material, and Temperature Range | Model<br>Number | Packing<br>Type | Package<br>Type |

| S30MS01GP                    | 25              | BAW, BFW                                      | 00, 01,         | 0, 3            | 137-Ball FBGA   |

| S30MS512P                    | 25              | TAW, TFW                                      | 50, 51          | (Note 1)        | TSOP-48         |

#### Notes:

- 1. Type 0 is standard. Specify other options as required.

- 2. See the MCP ORNAND data sheet for further package details.

- 3. Model Numbers 50 and 51 must use 2-bit detection, 1-bit correction for applications that require 100% error-free read performance.

- 4. Model Numbers 50 and 51 may have up to 2% invalid blocks.

- 5. Model Numbers 50 and 51 have a boot block (Block 0 is valid upon shipment and error-free through 1000 cycles).

# 8. Electrical Specifications

## 8.1 Absolute Maximum Ratings

| Parameter                          | Symbol              | Rating                        | Unit |

|------------------------------------|---------------------|-------------------------------|------|

| Voltage on any pin relative to Voc | V <sub>IN/OUT</sub> | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Voltage on any pin relative to Vss | V <sub>CC</sub>     | -0.5 to + 2.5                 | V    |

| Storage Temperature                | T <sub>STG</sub>    | -65 to +150                   | °C   |

| Operating Temperature              | T <sub>OPR</sub>    | -25 to +85 (Wireless)         | °C   |

| Temperature under bias             | T <sub>BIAS</sub>   | -65 to +125                   | °C   |

| Short circuit current              | los                 | 5                             | mA   |

#### Notes:

- 1. Minimum DC voltage is -0.6 V on input/output pins. During transitions, this level may undershoot to -2.0 V for periods <30 ns.

- 2. Maximum DC voltage on input/output pins is  $V_{CC}$  +0.3 V which, during transitions, may overshoot to  $V_{CC}$ +2.0 V for periods < 20 ns.

- 3. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### 8.2 Capacitance (Ta = 25°C, f = 1 MHz)

| Parameter<br>Symbol | Parameter<br>Description  | Test<br>Condition    | Тур. | Max. | Unit |

|---------------------|---------------------------|----------------------|------|------|------|

| C                   | Input Capacitance         | V <sub>IN</sub> = 0  | _    | 10   | pF   |

| C <sub>IN</sub>     | три Сараспансе            | V <sub>IN</sub> = 0  | _    | 10   | pF   |

| C <sub>IN2</sub>    | CE# pin Input Capacitance | V <sub>IN</sub> = 0  | _    | 17   | pF   |

| C <sub>IN3</sub>    | WE# pin Input Capacitance | V <sub>IN</sub> = 0  | _    | 32   | pF   |

| 0                   | Output Capacitance        | V - 0                | _    | 10   | pF   |

| C <sub>OUT</sub>    | Оприг Сараспапсе          | V <sub>OUT</sub> = 0 | _    | 10   | pF   |

#### Notes:

- 1. Test conditions  $T_a = 25$ °C, f = 1.0 MHz

- 2. Sampled, not 100% tested.

### 8.3 Valid Blocks

Valid Blocks are fully erased when the device is shipped from the factory. To identify blocks that are invalid at the time of shipment, the system must read the lowest address in the first two pages of the spare area. If a non-blank data pattern is read from either of these two addresses, the block is invalid.

| Parameter<br>Symbol | Parameter<br>Description | Density | Model Number | Min. | Max. | Unit   |

|---------------------|--------------------------|---------|--------------|------|------|--------|

|                     |                          | 512Mb   | 50, 51       | 502  | 512  | Blocks |

| N                   | Number of Valid Blocks   | 312IVID | 00, 01       | 512  | 512  | Blocks |

| N <sub>VB</sub>     | Number of Valid Blocks   | 1Gb     | 50, 51       | 1004 | 1024 | Blocks |

|                     |                          | IGD     | 00, 01       | 1024 | 1024 | Blocks |

# 8.4 Recommended DC Operating Conditions

| Parameter<br>Symbol | Parameter<br>Description | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------|------|------|------|------|

| V <sub>CC</sub>     | Power Supply Voltage     | 1.7  | 1.8  | 1.95 | V    |

| V <sub>SS</sub>     | Power Supply Voltage     | 0    | 0    | 0    | V    |

### 8.5 DC Characteristics

| Parameter<br>Symbol      | Parameter<br>Description                                                           | Test Conditions                                                                        | Min.                  | Тур. | Max.                  | Unit |

|--------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| I <sub>CC1</sub>         | V <sub>CC</sub> active read current (average during read cycle)                    | t <sub>RC</sub> = 25 ns,<br>I <sub>OUT</sub> = 0 mA                                    | _                     | 40   | 45                    | mA   |

| I <sub>CC2</sub>         | V <sub>CC</sub> current during data transfer from memory cell array to Page Buffer | _                                                                                      | _                     | 40   | 45                    | mA   |

| I <sub>CC3</sub>         | V <sub>CC</sub> current during data output                                         | t <sub>RC</sub> = 25 ns                                                                | _                     | 10   | 20                    | mA   |

| I <sub>CC4</sub>         | Program current (standard mode)                                                    | _                                                                                      | _                     | 60   | 75                    | mA   |

| I <sub>CC5</sub>         | Erase Current (standard mode)                                                      | _                                                                                      | _                     | 60   | 75                    | mA   |

| I <sub>SB1</sub>         | Stand-by Current (TTL)                                                             | CE# = V <sub>IH</sub> ,<br>WP# = PRE# = V <sub>IL</sub>                                | _                     | _    | 1                     | mA   |

| I <sub>SB2</sub>         | Stand-by Current (CMOS)                                                            | $CE\# = V_{CC} -0.2 \text{ V},$ $WP\# = PRE\# = 0.2 \text{ V}$ All other pins = -0.1 V | _                     | 10   | 60                    | μА   |

| ILI                      | Input Leakage Current                                                              | $V_{IN} = 0$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC} max$                                    | _                     | _    | ±1                    | μА   |

| I <sub>LO</sub>          | Output Leakage Current                                                             | $V_{OUT} = 0 \text{ to } V_{CC},$ $V_{CC} = V_{CC} \text{ max}$                        | _                     | _    | ±1                    | μА   |

| V <sub>IH</sub> (note 1) | Input High Voltage                                                                 |                                                                                        | V <sub>CC</sub> - 0.4 | _    | V <sub>CC</sub> + 0.2 | V    |

| V <sub>IL</sub> (note 2) | Input Low Voltage                                                                  | _                                                                                      | -0.3                  | _    | 0.4                   | V    |

| V <sub>OH</sub>          | Output High Voltage Level                                                          | $I_{OH} = -100 \mu A,$ $V_{CC} = V_{CC} min$                                           | V <sub>CC</sub> - 0.1 | _    | _                     | V    |

| V <sub>OL</sub>          | Output Low Voltage Level                                                           | $I_{OL} = 100 \mu A,$ $V_{CC} = V_{CC} min$                                            | _                     | _    | 0.1                   | V    |

| I <sub>OL</sub>          | Output Low Current (RY/BY#)                                                        | V <sub>OL</sub> = 0.1 V                                                                | 2                     | 4    | _                     | mA   |

#### Notes:

<sup>1.</sup>  $V_{IH}$  can overshoot to  $V_{CC}$  +0.4 V for durations of 20 ns or less.

<sup>2.</sup>  $V_{\rm IL}$  can undershoot to  $-0.4~{\rm V}$  for durations of 20 ns or less.

### 8.6 AC Characteristics

| Parameter<br>Symbols | Description                                                   | Min. | Max.   | Unit |

|----------------------|---------------------------------------------------------------|------|--------|------|

| t <sub>CLS</sub>     | CLE Setup Time                                                | -1   | _      | ns   |

| t <sub>CLH</sub>     | CLE Hold Time                                                 | 8    | _      | ns   |

| t <sub>CS</sub>      | CE# Setup Time                                                | 0    | _      | ns   |

| t <sub>CH</sub>      | CE# Hold Time                                                 | 8    | _      | ns   |

| t <sub>WP</sub>      | Write Pulse Width                                             | 25   |        | ns   |

| t <sub>ALS</sub>     | ALE Setup Time                                                | -1   |        | ns   |

| t <sub>ALH</sub>     | ALE Hold Time                                                 | 8    | _      | ns   |

| t <sub>DS</sub>      | Data Setup Time                                               | 15   | 1      | ns   |

| t <sub>DH</sub>      | Data Hold Time                                                | 8    |        | ns   |

| $t_{WC}$             | Write Cycle Time                                              | 40   |        | ns   |

| $t_{WH}$             | WE# High Hold Time                                            | 10   |        | ns   |

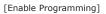

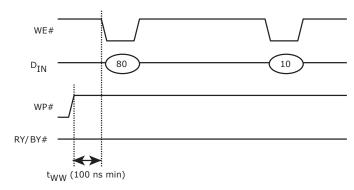

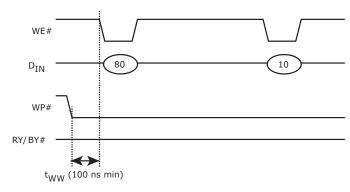

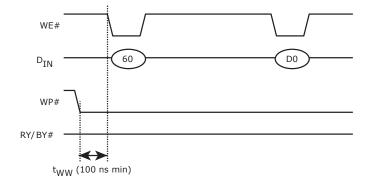

| $t_{WW}$             | WP# High to WE# Low                                           | 100  |        | ns   |

| t <sub>RR</sub>      | Ready to RE# Falling Edge                                     | 20   | 1      | ns   |

| $t_{RW}$             | Ready to WE# Falling Edge                                     | 20   |        | ns   |

| $t_{RP}$             | Read Pulse Width                                              | 17   |        | ns   |

| t <sub>RC</sub>      | Read Cycle Time                                               | 25   |        | ns   |

| t <sub>REA</sub>     | RE# Access Time                                               | _    | 17     | ns   |

| t <sub>CR</sub>      | CE# to RE# Time                                               | 10   |        | ns   |

| t <sub>AR</sub>      | ALE to RE# Time                                               | 10   |        | ns   |

| t <sub>CLR</sub>     | CLE to RE# Time                                               | 10   |        | ns   |

| t <sub>OH</sub>      | Data Output Hold Time                                         | 5    |        | ns   |

| $t_{RHZ}$            | RE# High to Output High Impedance                             | _    | 15     | ns   |

| t <sub>CHZ</sub>     | CE# High to Output High Impedance                             | _    | 15     | ns   |

| t <sub>REH</sub>     | RE# High Hold Time                                            | 8    |        | ns   |

| $t_{IR}$             | Output High Impedance to RE# Falling Edge                     | 0    |        | ns   |

| t <sub>RHW</sub>     | RE# High to WE# Low                                           | 30   |        | ns   |

| t <sub>WHC</sub>     | WE# High to CE# Low                                           | 30   |        | ns   |

| t <sub>WHR</sub>     | WE# High to RE# Low                                           | 60   |        | ns   |

| t-                   | Full Page Data Transfer from Memory Cell Array to Register    | _    | 25     | μs   |

| t <sub>R</sub>       | Partial Page Data Transfer from Memory Cell Array to Register | _    | 8      | μδ   |

| t <sub>RPRE</sub>    | Full page Data Transfer to Register During Power On Read      |      | 50     | μs   |

| t <sub>WB</sub>      | WE# High to Busy                                              | _    | 100    | ns   |

| t <sub>RST</sub>     | Device Resetting Time (Read/Program/Erase)                    | _    | 1/1/15 | μs   |

### 8.7 AC Test Conditions

| Operating Range                                               | V <sub>CC</sub> 1.7 V to 1.95 V |

|---------------------------------------------------------------|---------------------------------|

| Input level                                                   | 0.0 to V <sub>CC</sub>          |

| Input comparison level                                        | V <sub>CC</sub> /2              |

| Output data comparison level                                  | V <sub>CC</sub> /2              |

| Load capacitance (C <sub>L</sub> )                            | 30 pF                           |

| Transition time (t <sub>T</sub> ) (input rise and fall times) | 5 ns                            |

### 8.8 Program and Erase Characteristics

| Symbol              | Parameter                                                  | Min. | Typ.<br>(Note 4) | Max.<br>(Note 5) | Unit |

|---------------------|------------------------------------------------------------|------|------------------|------------------|------|

| t <sub>CBSY1</sub>  | Dummy Busy Time for Cache Programming (first 15h) (Note 2) | _    | 0.4              | 0.8              | μs   |

| t <sub>CBSY2</sub>  | Dummy Busy Time for Cache Programming (next 15h) (Note 3)  | _    | 0.8              | 4.4              | ms   |

| t <sub>PROG</sub>   | Page Programming Time                                      | _    | 0.8              | 4.4              | ms   |

| t <sub>PPROG</sub>  | Partial Page Programming Time                              | _    | 260              | 1400             | μs   |

| N                   | Number of Programming Cycles on Same Page (Note 1)         | _    | _                | 8                |      |

| t <sub>BERASE</sub> | Block Erasing Time                                         | _    | 50               | 150              | ms   |

#### Notes

- 1. One programming cycle per segment. Refer to Page Program on page 27 for more information.

- 2. First cache programming of a sequence.

- 3. Following cache programming of a sequence second page and following pages.

- 4. Typical program and erase times assume the following conditions: 25°C, 1.8 V V<sub>CC</sub>, 10,000 cycles; checkerboard data pattern.

- 5. Under worst case conditions of 90°C,  $V_{CC}$ =1.70 V, 100,000 cycles.

# 9. Timing Diagrams

Figure 9.1 Command Input Cycle Timing Diagram

Figure 9.2 Address Input Cycle Timing Diagram

Figure 9.3 Data Input Cycle Timing Diagram

Figure 9.4 Serial Read Cycle Timing Diagram

Figure 9.5 Status Read Cycle Timing Diagram

Figure 9.6 Read Cycle Timing Diagram

CLE tRHW  $t_{CR}$ WE# ALE RE#  $\overset{\longleftrightarrow}{t_{IR}}$ Col. Col. DOUT /DOUT I/O 05h E0h Add1 Add2 B+1 Column address Page address

Figure 9.8 Column Address Change in Read Cycle Timing Diagram (2/2)

Column address

В

RY/BY# Part A

Part B

Α

#### Notes:

- 1. If  $I/O \ 0 = 0$ , then the erase is successful. If  $I/O \ 0 = 1$ , then there is an error in the erase.

- 2. Only the block address part of the Row Address bytes are used; page address is ignored.

C E#

W E#

IVWB ICBSY2

W E#

IVWB ICBSY2

W E#

IVWB ICBSY2

W E#

IVWB ICBSY2

I

Figure 9.11 Cache Program Operation Timing Diagram

Note:

CE#, CLE, and ALE are Don't care.

CLE

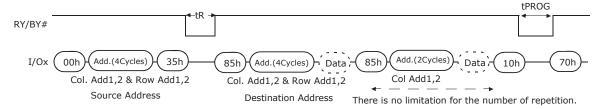

Figure 9.12 Page Duplicate Program Timing Diagram

Note:

CE#, CLE, and ALE are Don't care.

### 9.1 ID Read

Figure 9.13 ID Read Operation Timing Diagram

CE#, CLE, and ALE are Don't care.

Table 9.1 ID Byte Settings Summary

| Byte     |                                  | Description                            | Hex Data |

|----------|----------------------------------|----------------------------------------|----------|

| 1st Byte | Maker Code                       |                                        | 01h      |

|          |                                  | 512 Mb (x8)                            | 81h      |

| Ond Dute | 2nd Byte Device Code 1st Byte    | 512 Mb (x16)                           | 91h      |

| Zna Byte |                                  | 1 Gb (x8)                              | A1h      |

|          |                                  | 1 Gb (x16)                             | B1h      |

| Oud Dute | Device Ondo Ond Dide             | Model Numbers 50 and 51 (ECC Required) | 00h      |

| 3rd Byte | Device Code 2nd Byte             | Model Numbers 00 and 01                | 01h      |

| 4th Byte | Block Size, Simultaneous Progran | nmed Pages, RFU                        | 00h      |

| 5th Byte | Page Size, Spare Size, RFU       |                                        | 22h      |

#### Note:

In x16, I/O15 - I/O8 = 00h

Table 9.2 4th ID Byte

| Description                               |   |   | I/O6 | I/O5 | 1/04 | I/O3 | I/O2 | I/O1 | I/O0 |

|-------------------------------------------|---|---|------|------|------|------|------|------|------|

| Block Size: 128 KBytes                    |   | Х | Х    | Х    | Х    | Х    | 0    | 0    | 0    |

| Block Size: 512 KBytes                    |   |   | Х    | Х    | Х    | Х    | 0    | 0    | 1    |

| Block Size: 2048 KBytes                   |   |   | Х    | Х    | Х    | Х    | 0    | 1    | 0    |

|                                           | 1 | Х | Х    | Х    | 0    | 0    | Х    | Χ    | Х    |

| Number of simultaneously programmed pages | 2 | Х | Х    | Х    | 0    | 1    | Х    | Х    | Х    |

| Number of simultaneously programmed pages |   | Х | Х    | Х    | 1    | 0    | Х    | Х    | Х    |

| 8                                         |   |   | Х    | Х    | 1    | 1    | Х    | Χ    | Х    |

Table 9.3 5th ID Byte

| Description            | 1/07 | I/O6 | I/O5 | 1/04 | I/O3 | 1/02 | I/O1 | 1/00 |

|------------------------|------|------|------|------|------|------|------|------|

| Page Size: 512 KBytes  | Х    | Х    | Х    | Х    | Х    | 0    | 0    | 0    |

| Page Size: 1024 KBytes | Х    | Х    | Х    | Х    | Х    | 0    | 0    | 1    |

| Page Size: 2048 KBytes | Х    | Х    | Х    | Х    | Х    | 0    | 1    | 0    |

| Page Size: 4096 KBytes | Х    | Х    | Х    | Х    | Х    | 0    | 1    | 1    |

| Page Size: 8192 KBytes | Х    | Х    | Х    | Х    | Х    | 1    | 0    | 0    |

| Spare Size: 0 Bytes    | Х    | Х    | 0    | 0    | 0    | Х    | Х    | Х    |

| Spare Size: 8 Bytes    | Х    | Х    | 0    | 0    | 1    | Х    | Х    | Х    |

| Spare Size: 16 Bytes   | Х    | Х    | 0    | 1    | 0    | Х    | Х    | Х    |

| Spare Size: 32 Bytes   | Х    | Х    | 0    | 1    | 1    | Х    | Х    | Х    |

| Spare Size: 64 Bytes   | Х    | Х    | 1    | 0    | 0    | Х    | Х    | Х    |

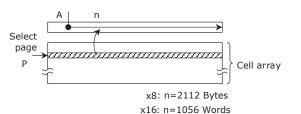

### 10. Schematic Cell Layout and Address Assignment

The Program operation works on page units while the Erase operation works on block units.

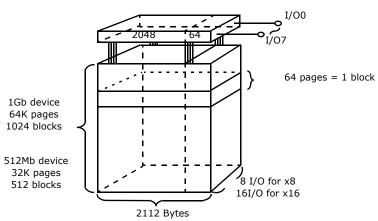

### 10.1 Array Organization

Figure 10.1 Array Organization

A page consists of 2112 Bytes in which 2048 Bytes are used for main memory storage and 64 Bytes are for redundancy or for other uses.

- 1 page = 2112 Bytes

- 1 block = 2112 Bytes x 64 pages = (128K + 4K) Bytes

- 1Gb density = 2112 Bytes x 64 pages x 1024 blocks

Table 10.1 shows a summary of the addressing for the memory array components.

Column Address **Row Address** Main Spare Colum Colum Block Page Main Spare Bus Addres Address Page Addres Page Addres in Block Density Width Main/Spare Area Segment Segment Blocks 1 Gb  $A_5:A_4$ 1024 х8 A<sub>17</sub>:A<sub>12</sub> A<sub>11</sub> (0=Main, 1=Spare) A<sub>27</sub>:A<sub>18</sub>  $A_{10}:A_{9}$  $A_8:A_0$  $A_3:A_0$ 1 Gb x16 A<sub>26</sub>:A<sub>17</sub> A<sub>16</sub>:A<sub>11</sub> A<sub>10</sub> (0=Main, 1=Spare) A<sub>9</sub>:A<sub>8</sub> A<sub>7</sub>:A<sub>0</sub> A<sub>4</sub>:A<sub>3</sub> A<sub>2</sub>:A<sub>0</sub> 1024 512 Mb х8 A<sub>26</sub>:A<sub>18</sub> A<sub>17</sub>:A<sub>12</sub> A<sub>11</sub> (0=Main, 1=Spare) A<sub>10</sub>:A<sub>9</sub> A<sub>5</sub>:A<sub>4</sub> 512 A<sub>8</sub>:A<sub>0</sub>  $A_3:A_0$ 512 Mb A<sub>4</sub>:A<sub>3</sub> x16 A<sub>25</sub>:A<sub>17</sub>  $A_{16}:A_{11}$ A<sub>10</sub> (0=Main, 1=Spare) A9:A8  $A_7:A_0$ 512  $A_2:A_0$

Table 10.1 Memory Addressing Key

An address is read through the I/O port over four consecutive clock cycles, as shown in Table 10.2 and Table 10.3. The Notes for Table 10.2 and Table 10.3 are listed below Table 10.3.

**Table 10.2** (1Gb) x 8 device

| 1Gbit     | I/O0            | I/O1            | I/O2            | I/O3            | I/O4            | I/O5            | 1/06            | 1/07            |

|-----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 1st Cycle | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>2</sub>  | A <sub>3</sub>  | A <sub>4</sub>  | A <sub>5</sub>  | A <sub>6</sub>  | A <sub>7</sub>  |

| 2nd Cycle | A <sub>8</sub>  | A <sub>9</sub>  | A <sub>10</sub> | A <sub>11</sub> | L<br>(Note 1)   | L<br>(Note 1)   | L<br>(Note 1)   | L<br>(Note 1)   |

| 3rd Cycle | A <sub>12</sub> | A <sub>13</sub> | A <sub>14</sub> | A <sub>15</sub> | A <sub>16</sub> | A <sub>17</sub> | A <sub>18</sub> | A <sub>19</sub> |

| 4th Cycle | A <sub>20</sub> | A <sub>21</sub> | A <sub>22</sub> | A <sub>23</sub> | A <sub>24</sub> | A <sub>25</sub> | A <sub>26</sub> | A <sub>27</sub> |

#### Table 10.3 (512Mb) x8 Addressing

| 512Mb     | I/O0            | I/O1            | I/O2            | I/O3            | I/O4            | I/O5            | 1/06            | 1/07            |

|-----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 1st Cycle | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>2</sub>  | A <sub>3</sub>  | A <sub>4</sub>  | A <sub>5</sub>  | A <sub>6</sub>  | A <sub>7</sub>  |

| 2nd Cycle | A <sub>8</sub>  | A <sub>9</sub>  | A <sub>10</sub> | A <sub>11</sub> | L<br>(Note 1)   | L<br>(Note 1)   | L<br>(Note 1)   | L<br>(Note 1)   |

| 3rd Cycle | A <sub>12</sub> | A <sub>13</sub> | A <sub>14</sub> | A <sub>15</sub> | A <sub>16</sub> | A <sub>17</sub> | A <sub>18</sub> | A <sub>19</sub> |

| 4th Cycle | A <sub>20</sub> | A <sub>21</sub> | A <sub>22</sub> | A <sub>23</sub> | A <sub>24</sub> | A <sub>25</sub> | A <sub>26</sub> | L<br>(Note 1)   |

#### Notes:

- 1.  $L = V_{IL}$

- 2. A0 to A11:Column address (12 bits for 2,112 Bytes). A12 to A27: Row address, consists of:

- A12 to A17: Page address in block (6 bits for 64 pages).

- 3. A18 to A27: Block address (1 Gb device: A18 to A27, 10 bits for 1024 blocks; 512Mb device: A18 to A26, 9 bits for 512 blocks.)

#### Table 10.4 (1Gb) x 16 Addressing

| 1Gb       | 1/00            | I/O1            | 1/02            | I/O3            | I/O4            | I/O5            | I/O6            | I/O7            | I/O8 – I/O15 |

|-----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------|

| 1st Cycle | $A_0$           | A <sub>1</sub>  | A <sub>2</sub>  | $A_3$           | A <sub>4</sub>  | A <sub>5</sub>  | A <sub>6</sub>  | A <sub>7</sub>  | L (Note 1)   |

| 2nd Cycle | A <sub>8</sub>  | A <sub>9</sub>  | A <sub>10</sub> | L (Note 1)      | L (Note 1)   |

| 3rd Cycle | A <sub>11</sub> | A <sub>12</sub> | A <sub>13</sub> | A <sub>14</sub> | A <sub>15</sub> | A <sub>16</sub> | A <sub>17</sub> | A <sub>18</sub> | L (Note 1)   |

| 4th Cycle | A <sub>19</sub> | A <sub>20</sub> | A <sub>21</sub> | A <sub>22</sub> | A <sub>23</sub> | A <sub>24</sub> | A <sub>25</sub> | A <sub>26</sub> | L (Note 1)   |

### **Table 10.5** (512) x 16 Addressing

| 512Mb     | I/O0            | I/O1            | 1/02            | I/O3            | I/O4            | I/O5            | I/O6            | 1/07            | I/O8 – I/O15 |

|-----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------|

| 1st Cycle | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>2</sub>  | $A_3$           | A <sub>4</sub>  | A <sub>5</sub>  | A <sub>6</sub>  | A <sub>7</sub>  | L (Note 1)   |

| 2nd Cycle | A <sub>8</sub>  | A <sub>9</sub>  | A <sub>10</sub> | L (Note 1)      | L (Note 1)   |

| 3rd Cycle | A <sub>11</sub> | A <sub>12</sub> | A <sub>13</sub> | A <sub>14</sub> | A <sub>15</sub> | A <sub>16</sub> | A <sub>17</sub> | A <sub>18</sub> | L (Note 1)   |

| 4th Cycle | A <sub>19</sub> | A <sub>20</sub> | A <sub>21</sub> | A <sub>22</sub> | A <sub>23</sub> | A <sub>24</sub> | A <sub>25</sub> | L (Note 1)      | L (Note 1)   |

#### Notes:

- 1.  $L = V_{IL}$

- 2. A0 to A1<sub>0</sub>:Column address (11 bits for 1,056 words)

- 3. A11 to A26: Row address, consists of:

- A11 to A16: Page address in block (6 bits for 64 pages).

- A17 to A26: Block address (1 Gb device:  $A_{17}$  to  $A_{26}$ : 10 bits for 1024 blocks; 512Mb device: A17 to A25: 9 bits for 512 blocks.)

### 11. Operation Mode: Logic and Command Tables

The operation modes such as Program, Erase, Read, and Reset are controlled by the thirteen different command operations shown in Table 11.2 on page 25. Address input, command input and data input/output are controlled by the CLE, ALE, CE#, WE#, RE# and WP# signals, as shown in Table 11.1.

Table 11.1 Operation Table

| CLE | ALE | CE# | WE# | RE# | PRE                 | WP#                 | Mode                          |                                |  |

|-----|-----|-----|-----|-----|---------------------|---------------------|-------------------------------|--------------------------------|--|

| Н   | L   | L   | Ţ   | Н   | Х                   | Х                   | Read Mode                     | Command Input                  |  |

| L   | Н   | L   | Ţ   | Н   | Х                   | Х                   | neau Mode                     | Address Input (4 clock cycles) |  |

| L   | L   | Х   | Н   | Н   | Х                   | Х                   | During Read (Busy)            |                                |  |

| L   | L   | L   | Н   | Ŧſ  | Х                   | Х                   | Sequential Read & Data Output |                                |  |

| Н   | L   | L   | Ţ   | Н   | Х                   | Н                   | Drogram Mada                  | Command Input                  |  |

| L   | Н   | L   | T   | Н   | X                   | Н                   | Program Mode                  | Address Input (4 clock cycles) |  |

| L   | L   | L   | Ţ   | Н   | Х                   | Н                   | Data Input                    |                                |  |

| Х   | Х   | Х   | Х   | X   | X                   | Н                   | During Program (Bus           | sy)                            |  |

| Х   | Х   | Х   | Х   | Х   | Х                   | Н                   | During Erase (Busy)           |                                |  |

| Х   | Х   | Х   | Х   | Х   | Х                   | L                   | Write Protect                 |                                |  |

| Х   | Х   | Н   | Х   | Х   | 0 V/V <sub>CC</sub> | 0 V/V <sub>CC</sub> | Stand-by                      |                                |  |

#### Notes:

- 1. H: V<sub>IH</sub>, L: V<sub>IL</sub>, X: V<sub>IH</sub> or V<sub>IL</sub>

- 2. WP# should be biased to CMOS high or CMOS low for standby.

Table 11.2 Command Table

| Function                             | 1st Cycle | 2nd Cycle | Command Accepted During Busy State |

|--------------------------------------|-----------|-----------|------------------------------------|

| Page Read                            | 00h       | 30h       | No                                 |

| Partial Page Read                    | 00h       | 31h       | No                                 |

| Read for Page Duplicate              | 00h       | 35h       | No                                 |

| ID Read                              | 90h       | _         | No                                 |

| Page Program                         | 80h       | 10h       | No                                 |

| Cache Program                        | 80h       | 15h       | No                                 |

| Page Duplicate Program               | 85h       | 10h       | No                                 |

| Data Input for Column Address Change | 85h       | _         | No                                 |

| Read for Column Address Change       | 05h       | E0h       | No                                 |

| Block Erase                          | 60h       | D0h       | No                                 |

| Reset                                | FFh       | _         | Yes                                |

| Status Read                          | 70h       | _         | Yes                                |

#### Notes:

- 1. Random Data Input/Output can be executed in a page or 1/4 page.

- 2. Input of a command other than those specified in Table 11.2 is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

- 3. During the Busy state, input commands are restricted to 70h and FFh.

**Table 11.3** Read Mode Operation Status

| Operation       | CLE | ALE | CE# | WE# | RE# | I/O0 to I/O15  | Power   |

|-----------------|-----|-----|-----|-----|-----|----------------|---------|

| Output Select   | L   | L   | L   | Н   | L   | Data Output    | Active  |

| Output Deselect | L   | L   | Х   | Н   | Н   | High Impedance | Active  |

| Standby         | Х   | Х   | Н   | Х   | Х   | High Impedance | Standby |

#### Notes:

1.  $H = V_{IH}$

2.  $L = V_{IL}$

3.  $X = V_{IH} \text{ or } V_{IL}$

### 12. Device Operation

#### 12.1 Read Mode

There are two types of read operations: random read and serial page read. The device defaults to Read mode after power-up or a Reset or may be initiated by writing 00h-30h to the command register along with four address cycles. A partial page read may be initiated by writing 00h-31h to the command register along with the four address cycles. The random data read is enabled by a page or partial page address change. The addressed page of data is loaded into the page register and the completion of the loading process is detected by polling the RY/BY# pin or reading the status register. Once the data is loaded into the page register, it may be read by clocking RE#. The high to low transition of the RE# signal outputs data sequentially, starting with the first selected column address and ending with the last selected column address. Subsequent reads will output the last column address data. See Figure 12.1 for timing details.

The device may output random data in a page instead of the consecutive sequential data upon entering the random data output command. The column address of the next data to be read can be changed to the address which follows the random data output command. The random data output command may be issued multiple times, but must be within the same page.

Figure 12.1 Read Mode

CLE

CE#

WE#

ALE

RE#

RY/BY#

Column Address A Page Address P

Start-address input

Busy

Page Address P

Page Address P

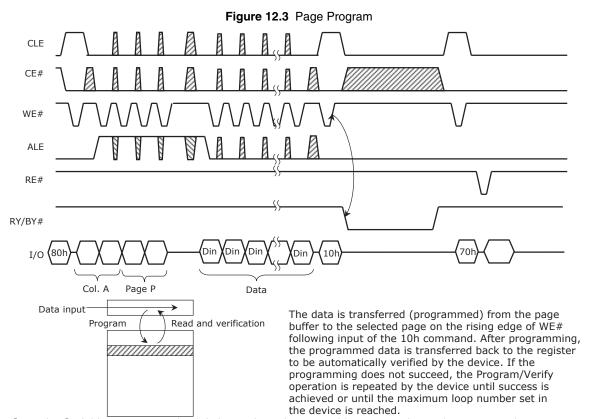

A data transfer operation from the cell array to the page buffer starts on the rising edge of WE# in the 30h command input cycle (after the address information has been latched). The device is in Busy state during this transfer period. After the transfer period the device returns to Ready state. Serial data can be output synchronously with the RE# clock from the start pointer designated in the address input cycle.

## 12.2 Page Program

The device conducts an Automatic Page Program operation when it receives a 10h Program confirm command after the address and data are input. The sequence of command and address and data input is shown below. (See Figure 12.3.)

Partial page programming is allowed for this device. A page is divisible into eight segments and each segment may be programmed individually or in any combination of segments simultaneously. For example, in x8 devices the first data segment of 512 bytes and the first spare area segment of 16 bytes, are programmable at the same time. Table 12.1 describes the page segments:

|             | x8                            | x16                           |

|-------------|-------------------------------|-------------------------------|

| Data Area   | 512 Bytes x 4 Segments / Page | 512 Bytes x 4 Segments / Page |

| 1st segment | Column Address 0 to 511       | Column Address 0 to 255       |

| 2nd segment | Column Address 512 to 1023    | Column Address 256 to 511     |

| 3rd segment | Column Address 1024 to 1535   | Column Address 512 to 767     |

| 4th segment | Column Address 1536 to 2047   | Column Address 768 to 1023    |

| Spare Area  | 16 Bytes x 4 Segments / Page  | 16 Bytes x 4 Segments / Page  |

| 1st segment | Column Address 2048 to 2063   | Column Address 1024 to 1031   |

| 2nd segment | Column Address 2064 to 2079   | Column Address 1032 to 1039   |

| 3rd segment | Column Address 2080 to 2095   | Column Address 1040 to 1047   |

| 4th segment | Column Address 2096 to 2111   | Column Address 1048 to 1055   |

Table 12.1 Page Segments

The maximum number of consecutive partial page program operations allowed in the same segment is one. Each of the eight segments may be programmed once before a block erase is required and each of the eight segments is independent with respect to the single program operation allowed.

The device also supports random data programming within a page by using the random data input command (85h). Random data input requires the command to be entered between column addresses during the page program command cycle. Once the new column address is entered, the system can continue the page

program command cycle by entering the page address and the data. The Page Program confirm command (10h) initiates the programming operation.

Once the program operation starts, the Read Status Register command may be entered to read the status register. The system controller can detect the completion of a **program** cycle by monitoring the RY/BY# output, or the Status bit (I/O6) of the Status Register. Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit (I/O0) may be verified. The internal write verify detects only errors for 1s that are not successfully programmed to 0s. The command register remains in Read Status command mode until another valid command is written to the command register.

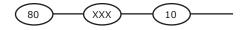

Once the Serial Input command 80h is input, the only acceptable commands are the programming commands 10h, 85h or the Reset command FFh. If any other input command is used, the program operation is not performed and the device must be reset.

Figure 12.4 Serial Input Command Sequence

#### Note

If XXX is a command other than 10h, 85h, or FFh, the operation does not execute. When this occurs, the reset command (FFH) must be entered to return the device to a valid state.

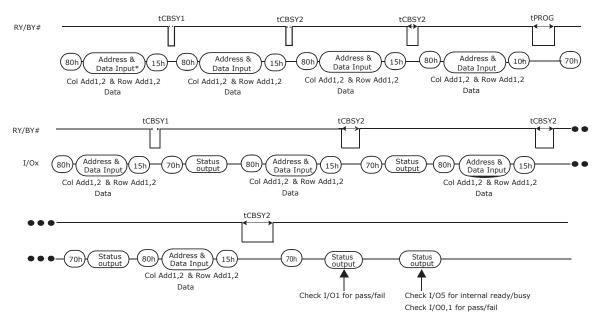

## 12.3 Cache Program

Cache Program is a double buffer scheme for faster programming. The Cache buffer size is identical to the page buffer size (i.e. 2112Byte (x8) or 1056Word (x16) data registers). Data may be written into the cache register while other data stored in the page buffer are programmed into the memory array.

After writing the first set of data up to 2112Byte (x8) or 1056Word (x16) into the cache register, the Cache program command (15h) must be entered instead of the standard Page Program command (10h) in order to free up the cache register and start the internal program operation. To transfer data from the cache register to the data register, the device remains in the Busy state for a short period of time ( $t_{CBSY}$ ) and has its cache register ready for the next data-input while the internal programming starts with the data loaded into the data

register. The Read Status command (70h) may be issued to verify that the cache register is ready by polling the Cache-Busy status bit (I/O6). Pass/Fail status of the previous page is available upon the return to the Ready state. When the next set of data is input with the Cache Program command, t<sub>CBSY</sub> is affected by the progress of pending internal programming. The programming of the cache register is initiated only when the pending program cycle is finished and the data register is available for the transfer of data from the cache register. The status bit (I/O5) for internal Ready/Busy may be polled to identify the completion of internal programming.

If the system monitors the progress of programming with RY/BY# only, the last page of the target programming sequence must be programmed with Page Program command (10h). Alternatively, if the last page to be programmed is accomplished using the Cache Program command (15h), status bit (I/O5) must be polled to verify that the last program is actually finished before starting other operations.

Following the Cache Program Command (15h), the pass/fail status information is available as follows:

- 1. I/O1 returns the status of the previous page (when ready or when the I/O6 bit is changing to a 1).

- 2. I/O0 returns the status of the current page (upon true ready, or when the IO5 bit is changing to a 1).

- 3. I/O0 and I/O1 may be read together.

Figure 12.5 Cache Program

#### Note:

Since programming the last page does not employ caching, the program time has to be that of Page Program. However, if the previous program cycle with the cache data has not finished, the actual program cycle of the last page is initiated only after completion of the previous cycle, which can be expressed as the following formula:  $t_{PROG} = Program$  time of last page + program time of the (last -1) page - (program command time + data loading time of last page).

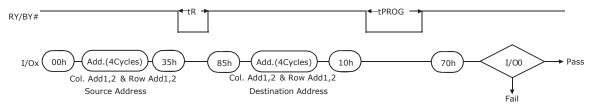

## 12.4 Page Duplicate Program